富士通研究所は2017年12月11日、WAN高速化の処理をFPGA(Field Programmable Gate Array)で高速化する技術を開発したと発表した。10Gbps回線で接続した実験環境において、CPUのみの処理に対して約30倍となる最大40Gbpsの実効転送速度を確認したという。本技術を搭載した製品は、2018年度中に富士通から提供することを目指す。

WAN高速化処理におけるデータ圧縮や重複排除のうち、負荷が重くCPUでの処理速度向上が難しい一部の処理をFPGAで実行する技術を開発した。CPUとFPGAアクセラレータを効率よく連携させることによって、効率よくWAN高速化を実現できるようにしたという。

FPGAを搭載したサーバーに今回開発した技術を適用したところ、CPUのみの処理に対して約30倍の高速化を確認したという。サーバー間を10Gbps回線で接続した実験環境を用意し、ドキュメントや画像データなどの定期的なバックアップを模擬した実験を実施したところ、最大40Gbpsの転送速度を確認したという。

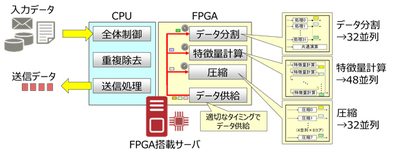

開発した技術の特徴は2つある。1つは、FPGAの並列化技術である。データ分割、特徴量計算、可逆圧縮処理に特化した専用演算器をFPGAに高並列に実装し、各演算の完了予測に基づいた適切なタイミングでデータを供給する。これにより、データの圧縮と重複排除に要する時間を大幅に削減できるという。

図1●FPGA並列化技術の概要(出所:富士通研究所)

図1●FPGA並列化技術の概要(出所:富士通研究所)拡大画像表示

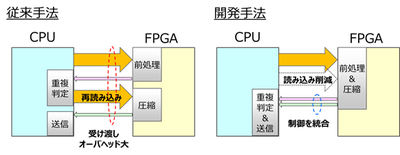

もう1つの特徴は、CPUとFPGAの間の処理フローを最適化する技術である。具体的には、最初にFPGA側で重複判定前処理と圧縮処理を行っておき、CPU側で重複判定結果に基づいて圧縮処理結果の反映を制御する処理手順とした。従来は、重複判定結果に基づいて可逆圧縮処理を行うかどうかを決定するため、FPGA側で実行する重複判定の前と後の処理で2度データを読む必要があり、オーバーヘッドが大きく十分な性能が出なかった。

図2●CPU-FPGA間の処理フロー最適化技術の概要(出所:富士通研究所)

図2●CPU-FPGA間の処理フロー最適化技術の概要(出所:富士通研究所)拡大画像表示

- 業務システム 2027年4月強制適用へ待ったなし、施行迫る「新リース会計基準」対応の勘所【IT Leaders特別編集版】

- 生成AI/AIエージェント 成否のカギは「データ基盤」に─生成AI時代のデータマネジメント【IT Leaders特別編集号】

- フィジカルAI AI/ロボット─Society 5.0に向けた社会実装が広がる【DIGITAL X/IT Leaders特別編集号】

- メールセキュリティ 導入のみならず運用時の“ポリシー上げ”が肝心[DMARC導入&運用の極意]【IT Leaders特別編集号】

- ゼロトラスト戦略 ランサムウェア、AI詐欺…最新脅威に抗するデジタル免疫力を![前提のゼロトラスト、不断のサイバーハイジーン]【IT Leaders特別編集号】

-

-

-

-

-

-

-

-

-

-

AIの真価は「今この瞬間」の感知にある。「Data Streaming Platform」で実現する「AI Ready Data」を解説

-

-

-

-

VDIの導入コストを抑制! コストコンシャスなエンタープライズクラスの仮想デスクトップ「Parallels RAS」とは

-

AI時代の“基幹インフラ”へ──NEC・NOT A HOTEL・DeNAが語るZoomを核にしたコミュニケーション変革とAI活用法

-

加速するZoomの進化、エージェント型AIでコミュニケーションの全領域を変革─「Zoom主催リアルイベント Zoomtopia On the Road Japan」レポート

-

14年ぶりに到来したチャンスをどう活かす?企業価値向上とセキュリティ強化・運用効率化をもたらす自社だけの“ドメイン”とは

-

-

-

-

生成AIからAgentic AIへ―HCLSoftware CRO Rajiv Shesh氏に聞く、企業価値創造の課題に応える「X-D-Oフレームワーク」

-

-

-

「プラグアンドゲイン・アプローチ」がプロセス変革のゲームチェンジャー。業務プロセスの持続的な改善を後押しする「SAP Signavio」

-

BPMとプロセスマイニングで継続的なプロセス改善を行う仕組みを構築、NTTデータ イントラマートがすすめる変革のアプローチ

-