大阪大学 量子情報・量子生命研究センターと富士通は2023年3月23日、現行コンピュータの計算性能を超える量子コンピュータの実用化を早める技術として「高効率位相回転ゲート式量子計算アーキテクチャ」を確立したと発表した。量子エラー訂正に必要な物理量子ビット数を大幅に低減する。現行の性能を超える64論理量子ビットの量子コンピュータを1万物理量子ビットで構築可能としている。

大阪大学 量子情報・量子生命研究センターと富士通は、現行コンピュータの計算性能を超える量子コンピュータの実用化を早める技術として「高効率位相回転ゲート式量子計算アーキテクチャ」を確立したと発表した(図1)。

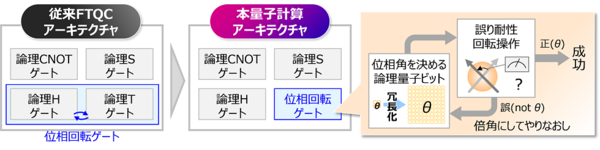

図1:大阪大学と富士通が確立した「高効率位相回転ゲート式量子計算アーキテクチャ」の概要(出典:大阪大学、富士通)

図1:大阪大学と富士通が確立した「高効率位相回転ゲート式量子計算アーキテクチャ」の概要(出典:大阪大学、富士通)拡大画像表示

富士通は、量子コンピュータが本来の性能を発揮するには、複数の物理量子ビットから1つの論理量子ビットを形成し、量子ビットに冗長性を持たせることで、発生した量子エラーを訂正しながら計算する量子エラー訂正技術がカギとなると説明している。

「従来のFTOC(Fault Tolerant Quantum Computer:誤り耐性量子コンピュータ)アーキテクチャでは、量子エラー訂正に100万以上の物理量子ビットが必要と言われている。物理量子ビット数が今後1万程度に到達した段階で量子エラー訂正を実行しても、計算可能な規模は極めて小さく、現行のコンピュータの処理能力を超えることは不可能と考えられていた」(富士通)

今回確立した量子計算アーキテクチャでは、従来のFTQCアーキテクチャとは異なる基本量子ゲートセットを新たに定義し、特に大量の物理量子ビットと量子ゲート操作が必要だった位相回転操作を高効率で実行する位相回転ゲートを世界で初めて導入する。

位相回転ゲートにより、物理量子ビットを従来の10分の1以下に低減し、任意回転の実行にかかるゲート操作回数を従来の20分の1程度に低減する。また、量子エラー確率は、物理量子ビットでの量子エラー確率の約8分の1まで抑えて高精度な計算を可能にする。 これらにより、現行コンピュータの最高性能の約10万倍に相当する64論理量子ビットの量子コンピュータを、1万物理量子ビットで構築が可能になるという。

- 業務システム 2027年4月強制適用へ待ったなし、施行迫る「新リース会計基準」対応の勘所【IT Leaders特別編集版】

- 生成AI/AIエージェント 成否のカギは「データ基盤」に─生成AI時代のデータマネジメント【IT Leaders特別編集号】

- フィジカルAI AI/ロボット─Society 5.0に向けた社会実装が広がる【DIGITAL X/IT Leaders特別編集号】

- メールセキュリティ 導入のみならず運用時の“ポリシー上げ”が肝心[DMARC導入&運用の極意]【IT Leaders特別編集号】

- ゼロトラスト戦略 ランサムウェア、AI詐欺…最新脅威に抗するデジタル免疫力を![前提のゼロトラスト、不断のサイバーハイジーン]【IT Leaders特別編集号】

-

-

-

-

-

-

-

-

-

-

AIの真価は「今この瞬間」の感知にある。「Data Streaming Platform」で実現する「AI Ready Data」を解説

-

-

-

-

VDIの導入コストを抑制! コストコンシャスなエンタープライズクラスの仮想デスクトップ「Parallels RAS」とは

-

AI時代の“基幹インフラ”へ──NEC・NOT A HOTEL・DeNAが語るZoomを核にしたコミュニケーション変革とAI活用法

-

加速するZoomの進化、エージェント型AIでコミュニケーションの全領域を変革─「Zoom主催リアルイベント Zoomtopia On the Road Japan」レポート

-

14年ぶりに到来したチャンスをどう活かす?企業価値向上とセキュリティ強化・運用効率化をもたらす自社だけの“ドメイン”とは

-

-

-

-

生成AIからAgentic AIへ―HCLSoftware CRO Rajiv Shesh氏に聞く、企業価値創造の課題に応える「X-D-Oフレームワーク」

-

-

-

「プラグアンドゲイン・アプローチ」がプロセス変革のゲームチェンジャー。業務プロセスの持続的な改善を後押しする「SAP Signavio」

-

BPMとプロセスマイニングで継続的なプロセス改善を行う仕組みを構築、NTTデータ イントラマートがすすめる変革のアプローチ

-