富士通研究所は2020年11月27日、サーバー仮想化基盤の上で動作する仮想アプライアンス型のルーター機器(仮想ルーター)を高速化する技術を開発したと発表した。ルーター機能をFPGAにオフロードして処理するとともに、性能のボトルネックとなっていたパケット宛先制御を高速化する技術を開発した。これにより、従来の仮想ルーターと比較して、パケット処理性能を約18倍高速化し、CPUリソースを約13分の1に削減した。2021年度中の実用化を目指す。

富士通研究所は今回、サーバー仮想化環境で動作する仮想ルーターを高速化する技術を開発した。プログラミング可能な集積回路であるFPGA(Field-Programmable Gate Array)にルーター機能の一部をオフロードすることでCPUの処理を肩代わりすると共に、パケットの宛先制御を高速化する。ネットワーク性能が高まり、ネットワーク処理に使うCPUリソースを削減できる。

検証では、オープンソースの代表的な仮想ルーター「Tungsten Fabric」を、FPGA「インテル Stratix 10 MX FPGA」上に実装し、汎用サーバー上でのオフロード効果を調査した。100Gbit/秒のEthernetで接続したサーバー2台で仮想サーバーを4台ずつ動かし、各仮想サーバー間で通信させた。従来手法では13.8Mbit/秒だったパケット処理性能が、250Mbit/秒と約18倍の高速化。また、使用CPUコア数も、従来の13コアから1コアに削減できた。

「今回開発した技術を用いることで、アプリケーションのサーバー集約率を向上させることができる。例えば、スタジアムにおける映像配信サービスが、より少ないサーバー台数で運用できるようになる」(富士通研究所)

開発の背景として同社は、1台の物理サーバー機に複数のアプリケーションとネットワーク処理機能を集約するサーバー仮想化が一般化する中、アプリケーションが取り扱うデータ量が増加傾向にあり、ネットワーク負荷の増大が問題となっている状況を挙げる。「仮想ルーターのパケット処理性能の向上と、ネットワーク処理に用いるCPUリソースの削減が課題となっている」(同社)という。

パケットの順序情報を保持して宛先制御を高速化

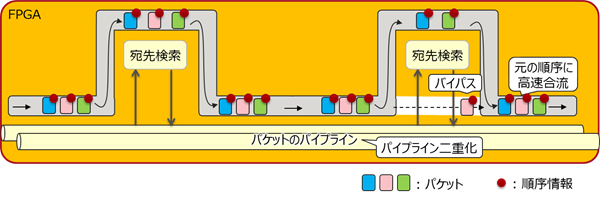

パケットの宛先制御を高速化する技術して、パケットの宛先を高速に検索する技術を開発した(図1)。従来は、パケット順を変更することなく全パケットで同じ処理を実施する手法をとっていた。ところが、この場合、仮想ルーター処理の入出力でパケット順が変わるとアプリケーションでは再送が発生し、品質低下やシステムの負荷増加につながってしまうという。

図1:パケットの宛先を高速に検索する技術の概要(出典:富士通研究所)

図1:パケットの宛先を高速に検索する技術の概要(出典:富士通研究所) 今回開発した技術では、パケットのパイプライン上で、パケットとは別に、パケットの順序情報を保持する。宛先検索処理において、前段検索の結果から不要となった次段検索をバイパスさせて合流させる際、パケットの順序情報を元にパケットを元の順序に戻す。パイプライン処理を高速に維持しつつメモリーアクセスを低減させると共に、パイプライン処理を2重化してパケット処理性能を向上させている。

高速なFPGA内部メモリーと大容量外部メモリーを使い分け

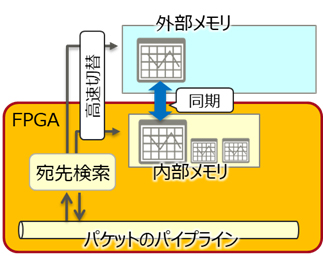

パケットの宛先制御を高速化するもう1つの技術が、検索テーブルをFPGAの内部メモリーと外部メモリーのハイブリッドメモリーで管理する技術である(図2)。宛先検索処理では、メモリー内にある複数のテーブルを検索して宛先を決定する。これに対して、高速で小容量なFPGAの内部メモリーと、大容量の外部メモリーとを、宛先検索処理を止めずに自動的に切り替える機能を開発した。

図2:宛先を検索する際に、高速なFPGA内部メモリーと大容量の外部メモリーを使い分けるハイブリッドメモリー管理技術の概要(出典:富士通研究所)

図2:宛先を検索する際に、高速なFPGA内部メモリーと大容量の外部メモリーを使い分けるハイブリッドメモリー管理技術の概要(出典:富士通研究所) 接続数の増加に伴って検索テーブル群のメモリー使用量が増加し、内部メモリーの空き容量が少なくなった場合に、容量あたりのアクセス頻度が低い検索テーブルをバックグラウンドで外部メモリーに同期しておき、検索処理を止めることなく外部メモリーの検索テーブルに自動で切り替える。これにより、通信先が多くて大きな検索テーブルが必要な場合でも、外部メモリーへのアクセスを抑え、安定したパケット処理性能を実現する。

- 業務システム 2027年4月強制適用へ待ったなし、施行迫る「新リース会計基準」対応の勘所【IT Leaders特別編集版】

- 生成AI/AIエージェント 成否のカギは「データ基盤」に─生成AI時代のデータマネジメント【IT Leaders特別編集号】

- フィジカルAI AI/ロボット─Society 5.0に向けた社会実装が広がる【DIGITAL X/IT Leaders特別編集号】

- メールセキュリティ 導入のみならず運用時の“ポリシー上げ”が肝心[DMARC導入&運用の極意]【IT Leaders特別編集号】

- ゼロトラスト戦略 ランサムウェア、AI詐欺…最新脅威に抗するデジタル免疫力を![前提のゼロトラスト、不断のサイバーハイジーン]【IT Leaders特別編集号】

-

-

-

-

-

-

-

-

-

-

-

-

AIの真価は「今この瞬間」の感知にある。「Data Streaming Platform」で実現する「AI Ready Data」を解説

-

-

-

-

VDIの導入コストを抑制! コストコンシャスなエンタープライズクラスの仮想デスクトップ「Parallels RAS」とは

-

AI時代の“基幹インフラ”へ──NEC・NOT A HOTEL・DeNAが語るZoomを核にしたコミュニケーション変革とAI活用法

-

加速するZoomの進化、エージェント型AIでコミュニケーションの全領域を変革─「Zoom主催リアルイベント Zoomtopia On the Road Japan」レポート

-

14年ぶりに到来したチャンスをどう活かす?企業価値向上とセキュリティ強化・運用効率化をもたらす自社だけの“ドメイン”とは

-

-

-

-

生成AIからAgentic AIへ―HCLSoftware CRO Rajiv Shesh氏に聞く、企業価値創造の課題に応える「X-D-Oフレームワーク」

-

-

-

「プラグアンドゲイン・アプローチ」がプロセス変革のゲームチェンジャー。業務プロセスの持続的な改善を後押しする「SAP Signavio」

-

BPMとプロセスマイニングで継続的なプロセス改善を行う仕組みを構築、NTTデータ イントラマートがすすめる変革のアプローチ

-