富士通は2018年8月22日、理化学研究所の「京」の後継機となるスーパーコンピュータに搭載するCPU「A64FX」の仕様を公表した。英ArmのArmv8-A命令セットアーキテクチャをスーパーコンピュータ向けに拡張する「SVE(Scalable Vector Extension)」を採用したCPUとなる。

富士通と理化学研究所は、2014年10月からスーパーコンピュータ「京」の後継機として、ポスト「京」の試作と詳細設計を進めている。2021年ころの共用開始を目指している。ポスト「京」の特徴の1つは、より幅広いユーザー層による利用を想定し、それまでのSPARCに代わってArmアーキテクチャを採用したことである。

写真1:「A64FX」のパッケージ写真

写真1:「A64FX」のパッケージ写真 富士通は今回、高性能プロセッサと関連技術に関するシンポジウム「Hot Chips 30」(米国で8月19日から21日にかけて開催)に参加し、ポスト「京」に搭載するCPUである「A64FX」の詳細を公表した。A64FXのアーキテクチャは、富士通がこれまでスーパーコンピュータやメインフレーム、UNIXサーバーで培った技術を発展させて開発した、としている。

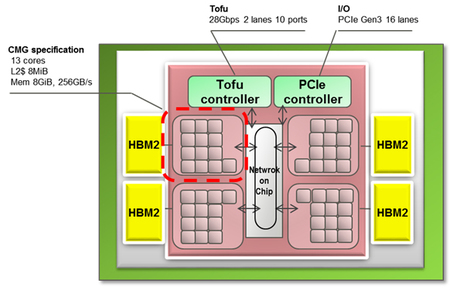

図1:「A64FX」のブロック図(出典:富士通)

図1:「A64FX」のブロック図(出典:富士通)拡大画像表示

A64FXの演算性能は、倍精度(64ビット)浮動小数点演算がピーク性能で2.7TFLOPS以上。単精度(32ビット)ではこの2倍、半精度(16ビット)では4倍の演算性能が得られる。16ビット整数、8ビット整数の演算性能も強化した。これにより、従来のスーパーコンピュータが得意とするコンピュータシミュレーションだけでなく、ビッグデータ処理や機械学習など、幅広い分野に適応できる。

データをメモリーからCPUに高速に転送できるように、高いメモリーバンド幅も確保している。これにより、CPUの演算処理部を効率よく利用でき、アプリケーションの実行性能を高められる。また、CPUとCPUの間を、「京」に向けて開発した独自のインターコネクト「Tofu」で直結し、並列性能を向上している。

| 項目 | 内容 |

|---|---|

| 命令セットアーキテクチャ | Armv8.2-A SVE(512-bit wide SIMD) |

| コア数 | 48コンピューティングコア、4アシスタントコア |

| メモリー | 32GiB(HBM2) |

| プロセステクノロジー | 7nm FinFET |

| トランジスタ数 | 約87億トランジスタ |

| ピーク性能(TOPS) | 倍精度(64ビット)浮動小数点演算:2.7 TOPS以上(DGEMM実行効率90%以上) 単精度(32ビット)浮動小数点演算:5.4 TOPS以上 半精度(16ビット)浮動小数点演算/16ビット整数演算:10.8TOPS以上 8ビット整数演算:21.6TOPS以上 |

| ピークメモリーバンド幅 | 毎秒1024GB(STREAM Triad実行効率80%以上) |

- 業務システム 2027年4月強制適用へ待ったなし、施行迫る「新リース会計基準」対応の勘所【IT Leaders特別編集版】

- 生成AI/AIエージェント 成否のカギは「データ基盤」に─生成AI時代のデータマネジメント【IT Leaders特別編集号】

- フィジカルAI AI/ロボット─Society 5.0に向けた社会実装が広がる【DIGITAL X/IT Leaders特別編集号】

- メールセキュリティ 導入のみならず運用時の“ポリシー上げ”が肝心[DMARC導入&運用の極意]【IT Leaders特別編集号】

- ゼロトラスト戦略 ランサムウェア、AI詐欺…最新脅威に抗するデジタル免疫力を![前提のゼロトラスト、不断のサイバーハイジーン]【IT Leaders特別編集号】

-

-

-

-

-

-

-

-

-

-

-

-

AIの真価は「今この瞬間」の感知にある。「Data Streaming Platform」で実現する「AI Ready Data」を解説

-

-

-

-

VDIの導入コストを抑制! コストコンシャスなエンタープライズクラスの仮想デスクトップ「Parallels RAS」とは

-

AI時代の“基幹インフラ”へ──NEC・NOT A HOTEL・DeNAが語るZoomを核にしたコミュニケーション変革とAI活用法

-

加速するZoomの進化、エージェント型AIでコミュニケーションの全領域を変革─「Zoom主催リアルイベント Zoomtopia On the Road Japan」レポート

-

14年ぶりに到来したチャンスをどう活かす?企業価値向上とセキュリティ強化・運用効率化をもたらす自社だけの“ドメイン”とは

-

-

-

-

生成AIからAgentic AIへ―HCLSoftware CRO Rajiv Shesh氏に聞く、企業価値創造の課題に応える「X-D-Oフレームワーク」

-

-

-

「プラグアンドゲイン・アプローチ」がプロセス変革のゲームチェンジャー。業務プロセスの持続的な改善を後押しする「SAP Signavio」

-

BPMとプロセスマイニングで継続的なプロセス改善を行う仕組みを構築、NTTデータ イントラマートがすすめる変革のアプローチ

-